# Testing Next-Gen Type-C Technologies of USB4, Thunderbolt 4, and DP 2.0

Jacky Yu

Project Manager / Keysight Technologies

#### Agenda

#### Preparing to test and avoid pitfalls in your USB4 implementations

- USB4/DPoC Overview

- USB4/DPoC Compliance Testing Overview

- USB4/DP Electrical Testing

- Q & A

#### Note:

- USB4<sup>™</sup>, USB Type-C<sup>™</sup> and USB-C<sup>™</sup> are trademarks of USB Implementers Forum

- Thunderbolt™ is a trademark of Intel Corporation

- VESA® is a registered trademark and DisplayPort™ is a trademark of VESA

- USB4 diagrams courtesy of the USB-IF

# USB4/DPoC Overview

#### **USB4** Overview

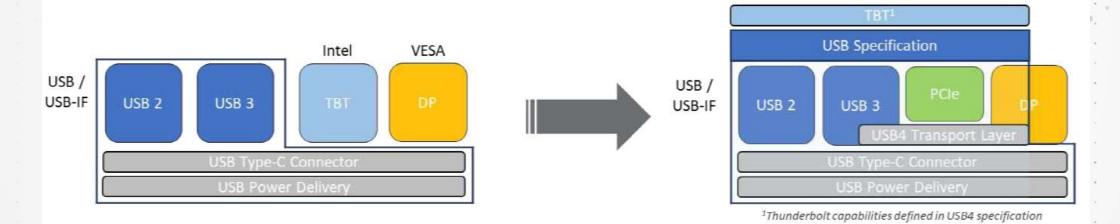

- Announced by USB-IF in March 2019

- Spec released September 2019

- Based on the Thunderbolt 3 protocol

- Open standard and potentially integrated in CPU

- Uses the Type-C connector

- Tunnels USB, DP, and PCIe

- Channel aggregation: two independent 20Gbps bonded into one logical 40Gbps link

- Supports other standards through ALT mode

- Keysight solution help test with early adopter Protocol Decode, TX, RX, and Return Loss

# Universal Serial Bus 4 (USB4™) Specification

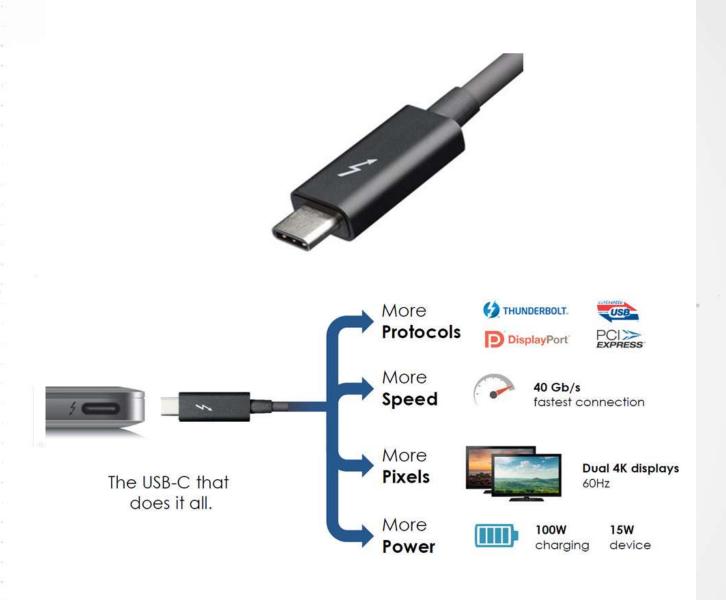

#### **Thunderbolt 3 Overview**

- Announced in Q2 2015

- Uses the Type-C connector

- Channel aggregation: two independent 20Gbps links into one logical 40Gbps link

- Supports other standards through ALT mode

- Cost competitive vs multi-chip, discrete, mux solutions

#### Thunderbolt and CIO (Converged IO)

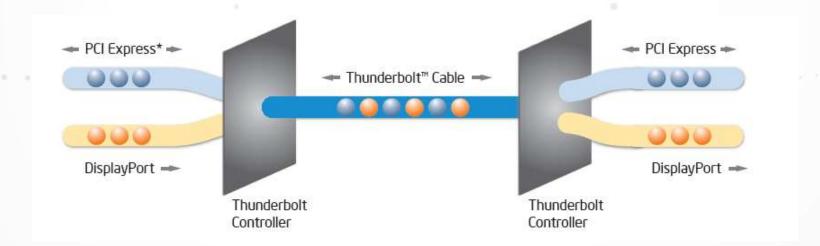

- Thunderbolt features two bidirectional (full duplex) channels that run up to 20Gbps each and allows daisy-chaining of up to six devices.

- Passive or active Cable

- Thunderbolt tunnels two protocols (PCI Express and DisplayPort) when running in native Thunderbolt mode.

#### **TBT4 Overview**

- To better align with USB4, Intel launch TBT4 in latest platform but provide same physical layer as TBT3.

- USB4 specification defines how to build TBT3 compatible products.

- Thunderbolt certification, brand names and logos are managed and owned by Intel without change.

#### **USB Revision Overview**

| Revision                 | Brand Name                 | Throughput        | Package Logo                            |

|--------------------------|----------------------------|-------------------|-----------------------------------------|

| USB1.1                   | Low Speed<br>Full Speed    | 1.5Mbps<br>12Mbps | USB                                     |

| USB2.0                   | High Speed                 | 480Mbps           | CERTIFIED USB                           |

| USB3.0<br>USB3.2 Gen 1x  | SuperSpeed USB<br>5Gbps    | 5Gbps             | SUPERSPEED USB                          |

| USB3.1<br>USB3.2 Gen 2x  | SuperSpeed USB<br>1 10Gbps | 10Gbps            | SUPERSPEED+                             |

| USB3.2<br>USB3.2 Gen 2x2 | SuperSpeed USB<br>20Gbps   | 20Gbps            | SUPERSPEED+                             |

| USB4<br>USB4 Gen 2x2     | USB4 20Gbps                | 20Gbps            | USB <sub>20</sub> <sup>TM</sup><br>Gbps |

| USB4<br>USB4 Gen 3x2     | USB4 40Gbps                | 40Gbps            | USB 40 TM Gbps                          |

Copyright © 2019, USB3.0 Promoter Group. All rights reserved.

## **Delivering the USB Type-C Vision**

- USB4<sup>™</sup> Specification Goals:

- Help converge USB Type-C connector ecosystem to minimize end-user confusion

- Drive broad adoption of USB4 architecture

- What the Specification Enables:

- Standards-based ownership for specifications and certification

- Third party vendors can build Thunderbolt™ 3 compatible SOC or peripheral silicon

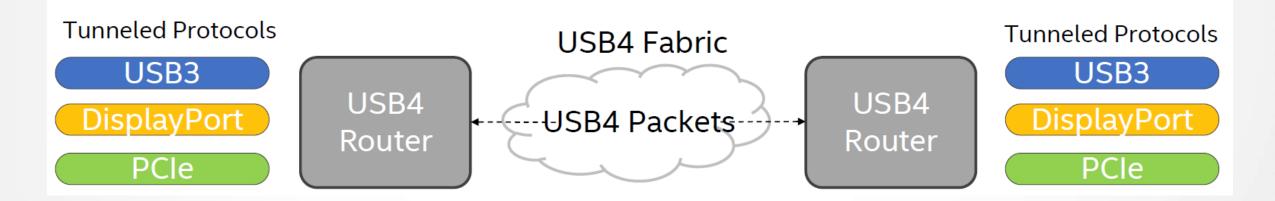

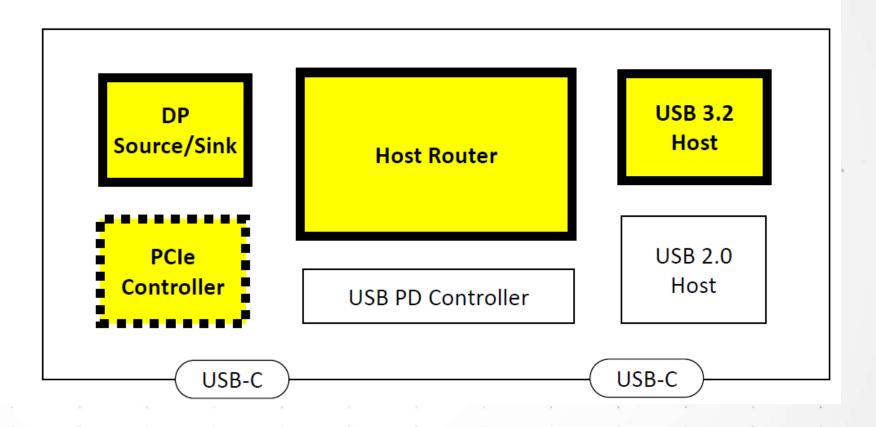

#### **USB4<sup>TM</sup> Architecture Overview**

- Runs over USB Type-C<sup>®</sup> interconnect

- Tunnels USB3, PCIe and DP protocols

- Signaling rates of 10 or 20 Gbps (10 to 40Gbps aggregated b/w)

- Utilizes passive and active cables (longer reach)

- Topologies with up to 6 routers

- Time sync accuracy support across USB4™ Fabric

#### What is DisplayPort?

- Digital display interface from GPU to display

- · Addresses embedded models as well

- Administered by VESA<sup>1</sup>

- Up to 4 differential lanes

- Daisy chain up to 32 monitors

- Connectors

- Standard DP

- Mini DP

- USB Type-C<sup>®</sup>

DPoC(Alt mode)

<sup>1</sup>Video Electronics Standards Association

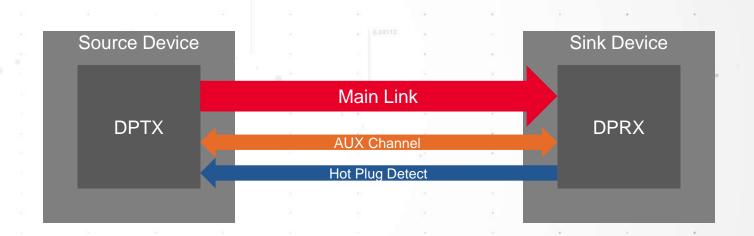

#### **DisplayPort Interface**

#### Main Link

- Display data transfer

- 4 unidirectional high-speed lanes

- Multiple bitrates supported

#### **AUX Channel**

- Link management

- Test mode control

- 1 bidirectional low-speed lane

#### **Hot Plug Detect**

- Source detects presence of sink

- Sink notifies of status changes via IRQ

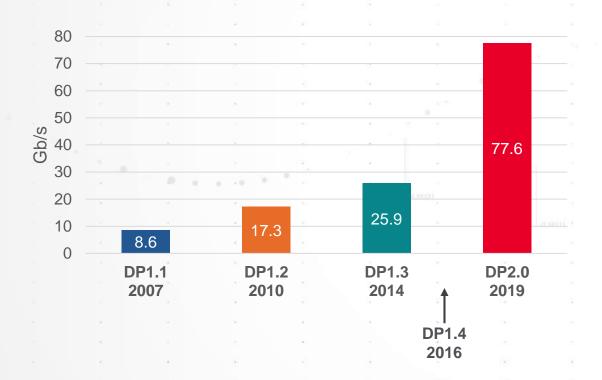

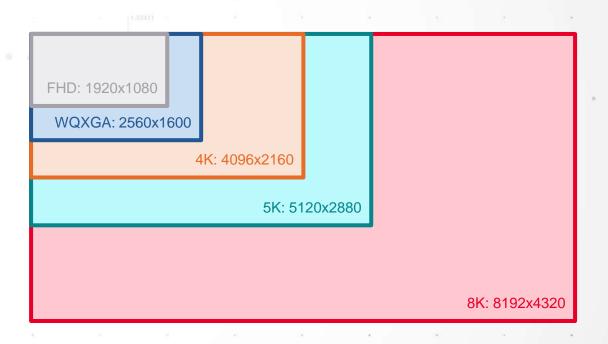

#### DP Maximum Data Transfer Rate and Resolution<sup>1</sup>

<sup>1</sup>Color depth = 24 bpp, refresh rate = 60 Hz

13

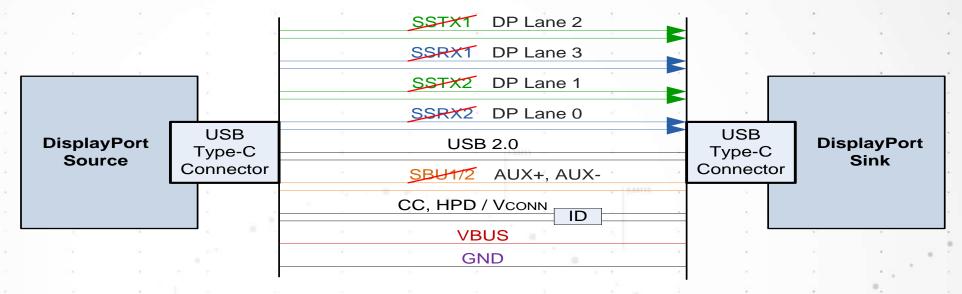

4xDP Over a USB Type-C to USB Type-C Full Feature Passive

Cable

- Utilizes optional DP Alt Mode capability of USB Type-C connector

- DisplayPort can use all four high speed lanes to deliver full DisplayPort performance

- The DisplayPort AUX Channel uses the SBU pins

- The DisplayPort HPD / IRQ is transmitted over the CC pin using the USB-PC protocol

- USB 2.0 and USB Power Delivery always available

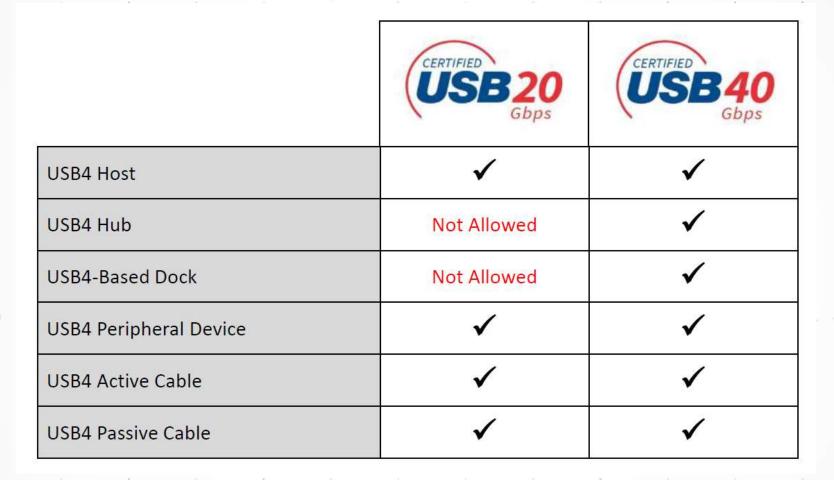

# **USB4™** Certification Categories

Copyright © 2019, USB3.0 Promoter Group. All rights reserved.

#### **USB4™** Required Testing – Hubs/Docks

- USB PD Compliance

- USB Type-C® Compliance

- USB 2.0 Compliance

- USB 3.2 Compliance

- USB4™ Compliance

- Tunneling

- TBT3-Compatibility

#### **USB4™** Required Testing – Hosts

- USB PD Compliance

- USB Type-C® Compliance

- USB 2.0 Compliance

- USB 3.2 Compliance

- USB4™ Compliance

- DP and USB3 Tunneling

- If supported:

- PCIe Tunneling

- TBT3-Compatibility

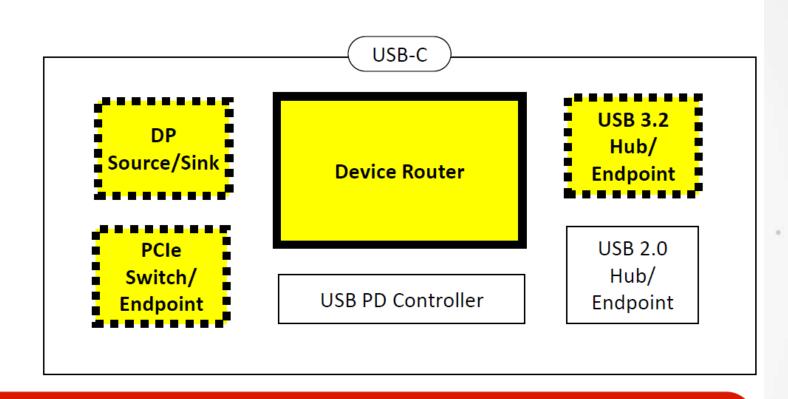

## **USB4™** Required Testing – Peripheral Devices

- USB PD Compliance

- USB Type-C® Compliance

- USB 2.0 Compliance

- USB 3.2 Compliance

- If supported

- USB4™ Compliance

- If supported:

- DP Tunneling

- USB3 Tunneling

- PCIe Tunneling

- TBT3-Compatibility

If support DP or PCle tunneling, must support equivalent USB function (if available)

## **DP Compliance Program**

- Managed by VESA

- Jim Choate (former Agilent USB Pyramid Lead)

- Why do companies need the logo?

- Ensure interoperability

- Consumers can easily identify compliant products

- How to get it?

- Pass the Compliance Program

- Be a member of VESA

- Sign the VESA DisplayPort Trademark License Agreement

- Authorized Test Centers (ATCs)

- · Allion, GRL, TTA, UL

#### **DP Compliance Test Specification**

- DP1.4a PHY CTS rev1.0 released in July 2018

- Ongoing activities to release new revision (2.0 coming soon)

- Several DUT types

- Source (un)tethered

- Sink (un)tethered

- Passive cables

- Others...

| Item | Name                                                                             | Normative/<br>Informative |

|------|----------------------------------------------------------------------------------|---------------------------|

| 3.1  | Eye Diagram Test                                                                 | Normative                 |

| 3.2  | HBR/RBR Non-PE Level Verification Test                                           | Normative                 |

| 3.3  | HBR/RBR PE Level Verification and Maximum Differential Peak-to-Peak Voltage Test | Normative                 |

| 3.4  | HBR3/HBR2 PE Level and Equalization Verification Test                            | Normative                 |

| 3.5  | HBR3/HBR2 V <sub>TX_DIFFp-p_MAX</sub> Test                                       | Normative                 |

| 3.6  | Inter-pair Skew Test                                                             | Informative               |

| 3.7  | Intra-pair Skew Test                                                             | Informative               |

| 3.8  | AC Common Mode Noise Test                                                        | Informative               |

| 3.9  | Non-ISI Jitter Measurement Test                                                  | Normative                 |

| 3.10 | HBR3 TX Differential RL Test                                                     | Informative               |

| 3.11 | TJ/RJ/DJ Measurement Tests                                                       | Normative                 |

| 3.12 | Main-Link Frequency Compliance Test                                              | Normative                 |

| 3.13 | Spread-spectrum Modulation Frequency Test                                        | Normative                 |

| 3.14 | Spread-spectrum Modulation Deviation Test                                        |                           |

| 3.15 | dF/dT Spread-spectrum Deviation High-frequency Variation Test                    | Informative               |

| Item | Name                                                                             | Normative/                |

| Item | Name      | Normative/<br>Informative |

|------|-----------|---------------------------|

| 4.1  | JTOL Test | Normative                 |

#### **DP Alt Mode Compliance Test Specification**

The DP Alt Mode on USB Type C CTS Version 1.0, was released Jan 24, 2017.

#### Over 200 DP Alt Mode products have been certified over last two years

Products include Sources, Sinks, Adapters and Docks

#### **DP Alt mode Certification Test Coverage**

#### Test plan and CTS covers all features and supported pin assignments.

- USB PD Compliance Testing

- Demonstration of proper functionality/behavior for DP Alt Modes

- A device must pass DP Alt Mode USB-PD certification tests to receive DP certification

- TX and RX Electrical testing of all supported modes with PHY test fixtures

- USB PHY electricals

- a. USB 3.2 5G

- b. USB 3.2 10G (if supported)

- c. USB 2.0 480Mb/s

- DP PHY electricals (DP 1.4a PHY CTS)

- RBR, HBR, HBR2, HBR3

- Aux Channel

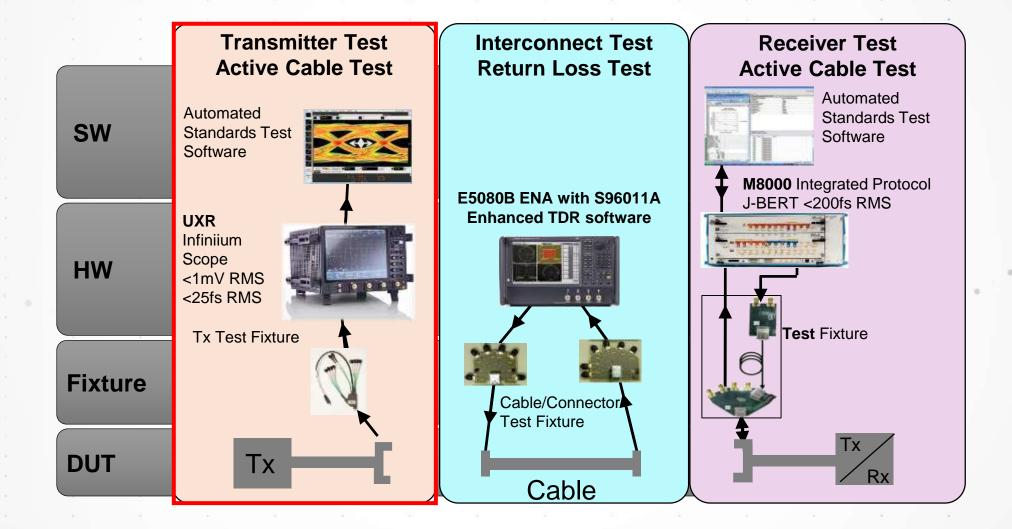

#### **USB4 Electrical Testing Methodology**

- PHY testing approach will be similar to Thunderbolt 3

- Tx, Rx, and Return Loss

- Active and Passive Cable Test

#### Plus

- Type-C Power Delivery

- DP, USB over Type-C

**Universal Serial Bus 4 (USB Type-C) Electrical Compliance Test Specification**  Universal Serial Bus 4 (USB Type-C)

Router Assembly

Electrical Compliance Test Specification

Date:

Jan 30, 2020

Revision:

0.9

25

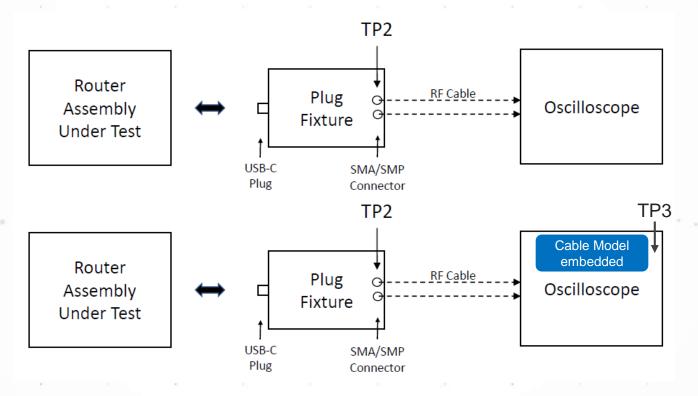

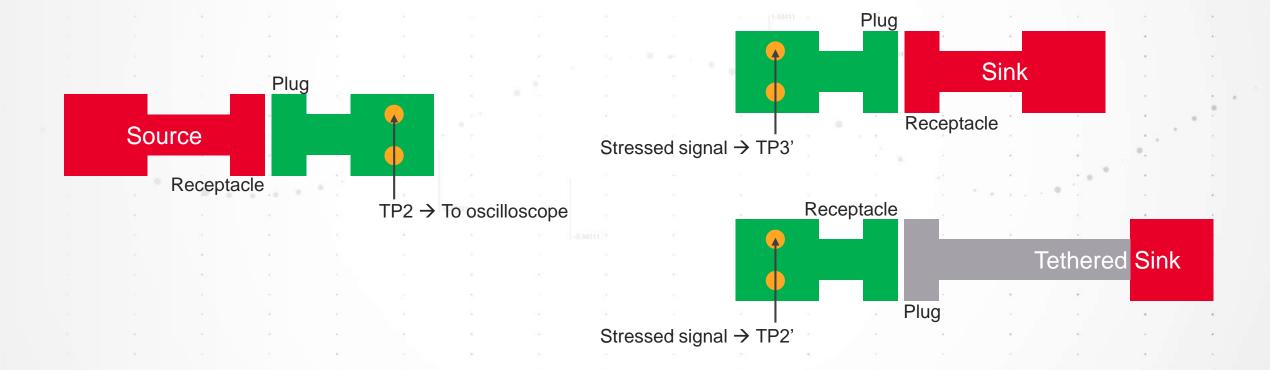

#### **Transmitter Measurement Point/Setup**

- TP2 measurements are done using plug-fixture

- TP3 measurements are done using plug-fixture with cable model embedded in the oscilloscope

Copyright © 2019, USB Implementers Forum.

# **Transmitter Specifications**

- Traditional voltage, eye, SSC, 10ps min rise/fall time

- Traditional UI, TJ, DDJ jitter decomposition

- Challenge: New Uncorrelated jitter measurements

Table 3-3. Transmitter Specifications Applied for All Speeds (at TP2)

| Symbol                      | Description.                                                                                                    | Min                              | Man                       | Units  | Conditions                                             |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|--------|--------------------------------------------------------|

| RL_DIFF                     | Differential Return Loss,<br>0.05-12GHz                                                                         |                                  | See<br>Section<br>3.4.1.2 | dB     |                                                        |

| RL_COMM                     | Common Mode Return<br>Loss, 0.05 - 126Hz                                                                        |                                  | See<br>Section<br>3.4.1.3 | 411    |                                                        |

| TX_EQ                       | Transmitter Equalization<br>Setting                                                                             | it.                              | See<br>Section<br>3.4.1.4 |        |                                                        |

| SSC_DOWN_SPREAD_RANGE       | Dynamic range of SSC<br>down-spreading during<br>steady-state                                                   | 0.4                              | 0.5                       | 56     | See Note 3.<br>Note 4, and<br>Figure 3-3.              |

| SSC_DOWN_SPREAD_RATE        | SSC down-spreading<br>modulation rate during<br>steady-state                                                    | 30                               | 33                        | XHz    | See Note 4 and<br>Figure 3-9.                          |

| ISC_PHASE_DEVIATION         | Phase jitter amonisted<br>with the SSC modulation<br>during steady state                                        | 2.5                              | 38.                       | 28 20  | See Note 1.<br>Note 4, and<br>Figure 2-9.              |

| ISC_SLEW_RATE               | SSC frequency slew rate (df/dt) during steady.                                                                  | -                                | 1250                      | ppm/ps | See Sote 2.<br>Note 4, and<br>Figure 1-8.              |

| TE_FREQ_VARIATIONS_TRAINING | TX frequency variation<br>during Link training,<br>before obtaining steady-<br>state                            | T                                | See<br>Sertion<br>3.4.1.1 | ppm    | See Note 4.                                            |

| LANE_TO_LANE_SKEW           | Skew between dual<br>transmit zignals of the<br>same USB4 Port                                                  | Ť.                               | 26                        |        | See Water S.                                           |

| RISE_FALL_TIME              | TX rise/fall time<br>measured between 20-<br>80% levels                                                         | 10                               | -                         | 34     | Test pattern<br>shall be SQ228<br>(see Table<br>6-56). |

| v_elec_inle                 | Feak voitage during<br>transmit electrical idle<br>(one-sided voltage<br>opening of the differential<br>signal) |                                  | 30                        | miV    | See Note 6.                                            |

| V_TX_DC_AC_CONN             | Instantaneous DC-AC<br>voltages at the connector<br>side of the AC coupling<br>capacitors                       | -0.5<br>(min1)<br>-0.3<br>(min2) | 1,0                       | v)     | See Nate 7.                                            |

TJ DDJ DCD(OE)

Table 3-6. Gen 2 Transmitter Specifications at TP2

| Symbol | Description                                                                           | Min   | Max    | Units | Comments                                                                                                                               |

|--------|---------------------------------------------------------------------------------------|-------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| UI     | Minimum Unit Interval                                                                 | 99.97 | 100.03 | ps    | The minimum UI value corresponds to the Link baseline speed of 10.0 Gbps with an uncertainty range of -300 ppm to 300 ppm. See Note 4. |

| AC_CM  | TX AC Common Mode voltage                                                             |       | 100    | mV pp |                                                                                                                                        |

| TJ     | Total Jitter                                                                          |       | 0.38   | UI pp | See Note 2 and Note 3.                                                                                                                 |

| UJ     | Sum of uncorrelated DJ and RJ<br>components (all jitter<br>components except for DDJ) |       | 0.31   | UI pp | See Note 2.                                                                                                                            |

| DDJ    | Data-Dependent Jitter                                                                 |       | 0.15   | UI pp | See Note 5.                                                                                                                            |

| UDJ    | Deterministic jitter that is<br>uncorrelated to the transmitted<br>data               |       | 0.17   | UI pp |                                                                                                                                        |

| UDJ_LF | Low Frequency Uncorrelated<br>Deterministic Jitter                                    |       | 0.04   | UI pp | See Note 6.                                                                                                                            |

| DCD    | Even-odd jitter associated with<br>Duty-Cycle-Distortion                              |       | 0.03   | UI pp |                                                                                                                                        |

| Y1     | TX eye inner height (one-sided<br>voltage opening of the<br>differential signal)      | 140   |        | mV    | Measured for 1E6 UI. See<br>Note 1, Note 2, and Figure<br>3-15.                                                                        |

| Y2     | TX eye outer height (one-sided<br>voltage opening of the<br>differential signal)      |       | 650    | mV    | Measured for 1E6 UI. See<br>Note 1, Note 2, and Figure<br>3-15.                                                                        |

pre 3-15. TX Mask Netations

#### **Return Loss**

- TX and RX return loss

- Differential and Common Mode Return Loss

- Challenge: Jumping straight into TX and RX testing

Figure 3-10. TX Differential Return Loss Mask

E5080B New ENA Network Analyzer

Figure 3-11. TX Common-Mode Return Loss Mask

KEYSIGHT

28

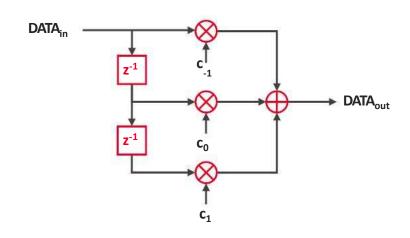

#### **Transmitter Equalization**

- Going from 1 pre-shoot and 1 de-emphasis to 16 presets, including a low-voltage variant

- Must test each preset, and also find optimal preset

- Challenge: Over-look optimization, or set incorrectly in TX silicon.

Table 3-5. Transmit Equalization Presets

| Preset Number | Pre-shoot [dB] | De-emphasis [dB] | Informative Filter Coefficients |                |                |  |

|---------------|----------------|------------------|---------------------------------|----------------|----------------|--|

| Freset Number |                |                  | C-1                             | C <sub>0</sub> | C <sub>1</sub> |  |

| 0             | 0              | 0                | 0                               | 1              | 0              |  |

| 1             | 0              | -1.9             | 0                               | 0.90           | -0.10          |  |

| 2             | 0              | -3.6             | 0                               | 0.83           | -0.17          |  |

| 3             | 0              | -5.0             | 0                               | 0.78           | -0.22          |  |

| 4             | 0              | -8.4             | 0                               | 0.69           | -0.31          |  |

| 5             | 0.9            | 0                | -0.05                           | 0.95           | 0              |  |

| 6             | 1.1            | -1.9             | -0.05                           | 0.86           | -0.09          |  |

| 7             | 1.4            | -3.8             | -0.05                           | 0.79           | -0.16          |  |

| 8             | 1.7            | -5.8             | -0.05                           | 0.73           | -0.22          |  |

| 9             | 2.1            | -8.0             | -0.05                           | 0.68           | -0.27          |  |

| 10            | 1.7            | 0                | -0.09                           | 0.91           | 0              |  |

| 11            | 2.2            | -2.2             | -0.09                           | 0.82           | -0.09          |  |

| 12            | 2.5            | -3.6             | -0.09                           | 0.77           | -0.14          |  |

| 13            | 3.4            | -6.7             | -0.09                           | 0.69           | -0.22          |  |

| 14            | 3.8            | -3.8             | -0.13                           | 0.74           | -0.13          |  |

| 15            | 1.7            | -1.7             | -0.05                           | 0.55           | -0.05          |  |

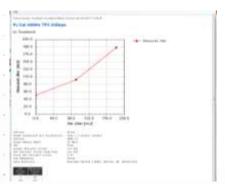

## **Transmitter Specifications at TP3**

- Use case for 0.8m or 2m cable

- Challenge: Can be most difficult test case, coupled with no channel test case.

Table 3-9. Gen 3 Transmitter Specifications at TP3

| Symbol | Description                                                                           | Min | Max  | Units | Comments                                                        |

|--------|---------------------------------------------------------------------------------------|-----|------|-------|-----------------------------------------------------------------|

| TJ     | Total Jitter                                                                          |     | 0.60 | UI pp | See Note 2, Note 3.                                             |

| UJ     | Sum of uncorrelated DJ and RJ<br>components (all jitter<br>components except for DDJ) |     | 0.31 | UI pp | Note 2.                                                         |

| UDJ    | Deterministic jitter that is<br>uncorrelated to the transmitted<br>data               |     | 0.17 | UI pp |                                                                 |

| X1     | TX eye horizontal deviation                                                           |     | 0.23 | UI    | Measured for 1E6 UI. See<br>Note 2, Note 4, and Figure<br>3-15. |

| Y1     | TX eye inner height (one-sided<br>voltage opening of the<br>differential signal)      | 49  |      | mV    | Measured for 1E6 UI. See<br>Note 1, Note 2, and Figure<br>3-15. |

| Y2     | TX eye outer height (one-sided<br>voltage opening of the<br>differential signal)      |     | 650  | mV    | Measured for 1E6 UI. See<br>Note 1, Note 2, and Figure<br>3-15. |

#### Notes:

- 1. TX voltage is differential.

- Measured while applying the reference CDR described in Section 3.3.3 and the reference equalizer

defined in Section 3.3.4. Note that the measured jitter includes residual SSC jitter passing the reference

CDR

- TJ is defined as the sum of all "deterministic" components plus 14.7 times the RJ RMS (the transmitter RJ RMS multiplier corresponds to the target BER with some margin on top).

- X1 specification is informative but shall be assumed as a valid reference if direct TJ measurement cannot be reliably performed.

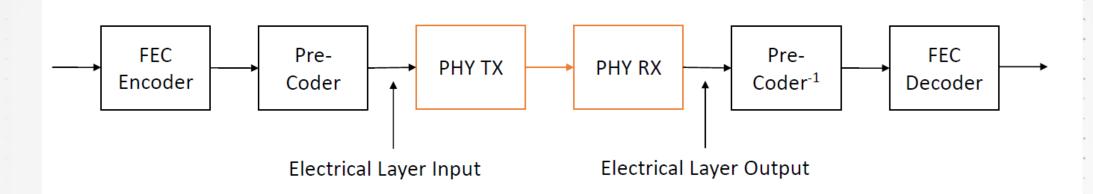

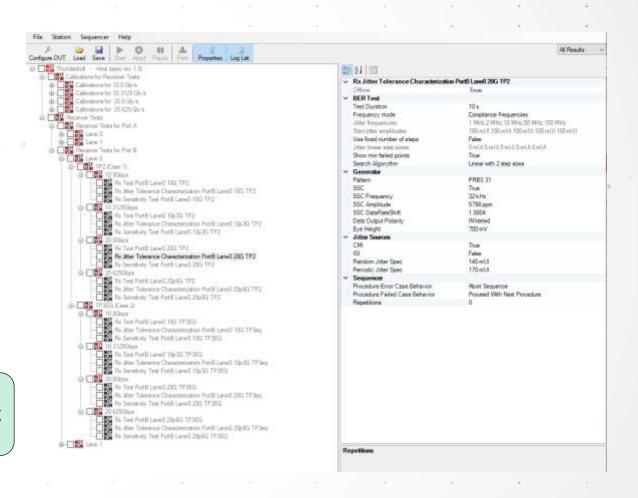

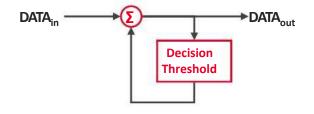

## **USB4<sup>TM</sup> RX Testing Methodology**

- The Electrical performance is tested in stand-alone mode without applying Pre-Coding nor Forward-Error-Correction

- The testing is based on PRBS patterns driven by pattern-generator

- The coded BER performance cannot be measured directly due to the large measurement window needed (several years...) and therefore validated indirectly based on electrical layer indicators

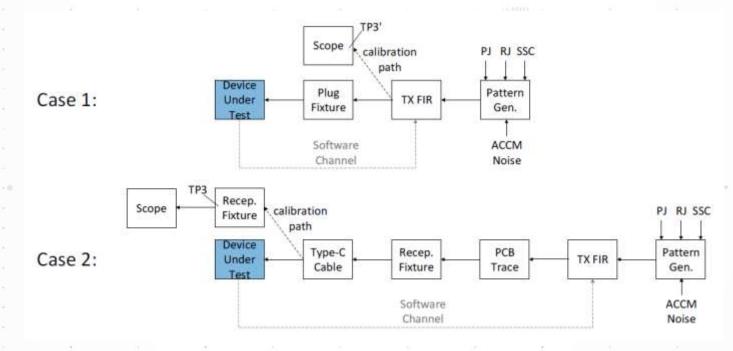

#### **Receiver Uncoded BER**

- The receiver shall operate at uncoded BER of 1E-12 with stressed signal applied

- Two test setups are used for evaluating the receiver tolerance:

- "Case1" addressing installations with low insertion-loss

- "Case2" addressing installations with maximum insertion-loss

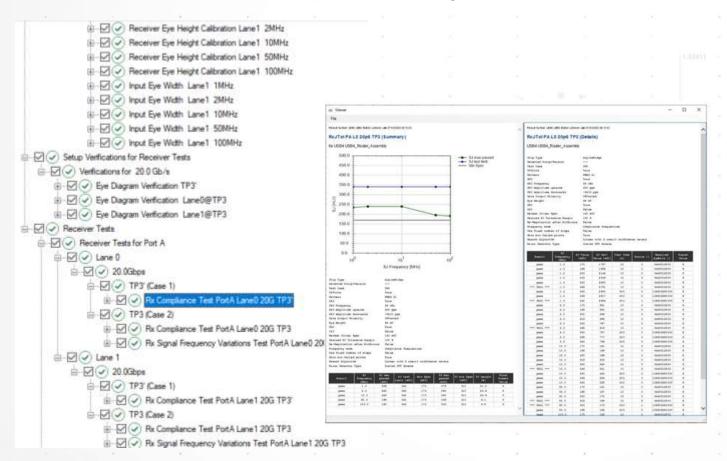

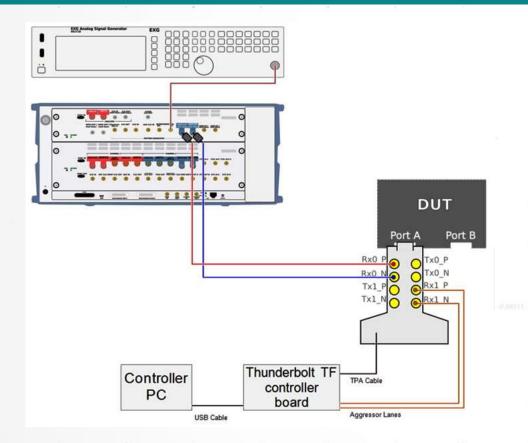

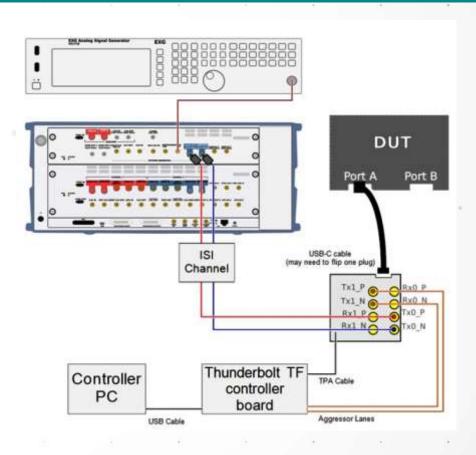

#### **USB4 Electrical Receiver Test Proposal**

- Support Both M8020A and M8040A BERT

- N5991U40A USB4 Receiver Compliance Test Software

M8020A J-BERT + M8062A 32Gbps MUX

M8040A 32/64 Gbaud J-BERT

# USB4 Test Setup (M8020A): Calibration for Case 1 and Case 2

Case 1 (Near End) Case 2 (Far End)

# USB4 Receiver Test Calibration for 10Gb/s, 10.3125Gb/s, 20Gb/s and 20.625 Gb/s

#### THUNDERBOLT CTS V1.5 SECTION 4.2

- 1. Select TX Equalization Preset for TP2 (Case 1)

- 2. Calibrate AC Common Mode for TP2 (Case 1)

- 3. Calibrate Random Jitter for TP2 (Case 1)

- Calibrate Total Jitter at TP2 (Case 1) for all PJ frequencies: 1 MHz, 2 MHz, 10 MHz, 50 MHz and 100 MHz

- Calibrate Eye Diagram at TP2 (Case 1) for all PJ frequencies: 1 MHz, 2 MHz, 10 MHz, 50 MHz and 100 MHz

- 6. Calibrate Total Jitter at TP3EQ (Case 2) for all PJ frequencies: 1 MHz, 2 MHz, 10 MHz, 50 MHz and 100 MHz

- Calibrate Eye Diagram at TP3EQ (Case 2) for all PJ frequencies: 1 MHz, 2 MHz, 10 MHz, 50 MHz and 100 MHz

# USB4 Test Setup (M8020A): Case 1 and Case 2 Execution

#### Case 1 (Near End)

#### Case 2 (Far End)

## **USB4** Receiver Test Execution

#### THUNDERBOLT CTS V1.5 SECTION 4.3

- Connect the DUT for Receiver testing.

- Recall Test Case 1 calibrated setup that was saved previously.

- 3. Negotiate Equalization Preset with the DUT

- 4. Run BER Test for 400s (Gen2) or 200s (Gen3)

- 5. If Error count >0, repeat step 4 but for 700s (Gen2) or 350s (Gen3)

- 6. If Error Count >2, FAIL the test, otherwise PASS

- 7. Repeat steps 2 to 6 for Test Case 2

- 8. Repeat steps 2 to 7 for all ports, speeds and PJ settings

Keysight provides simple, repeatable automated and unattended calibration and test execution using automation SW for Tx and Rx Test

37

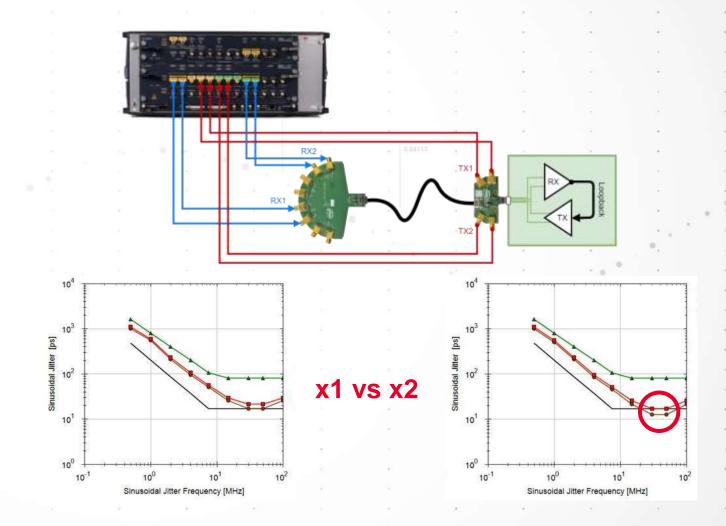

## **USB3.2 x 2 Receiver Testing (BKM)**

- Two Pattern Generators / Error Detectors

- Two independent RX paths fully calibrated

- Link Training in x2 mode

- Concurrent JTOL on both RX lanes

- USB-like traffic during test

- Test setup like operating conditions

38

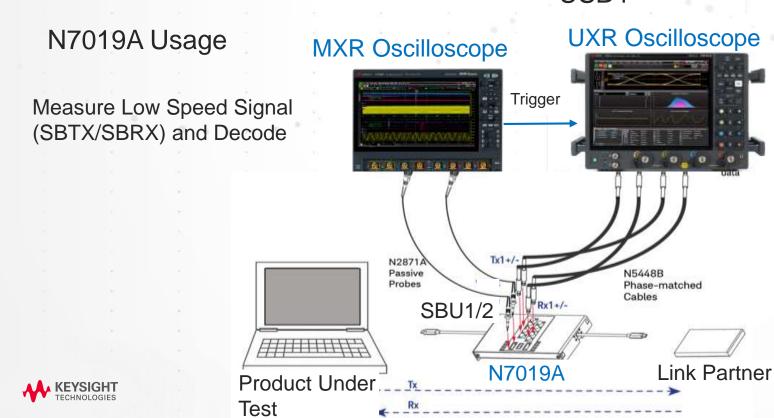

## N7019A USB Type-C Active Link Test Fixture

Provides access to all Type-C signals during an active link Signals include Vbus, USB 2.0, USB-PD, SBU1/2, and TX/RX up to maximum USB4 rate of 20 Gbps

Works in conjunction with Keysight Protocol Trigger Decode solutions for USB-PD, USB 2.0, USB 3.2, and USB4

Measure High Speed Signal (TX1/RX1,TX2/RX2) and Decode

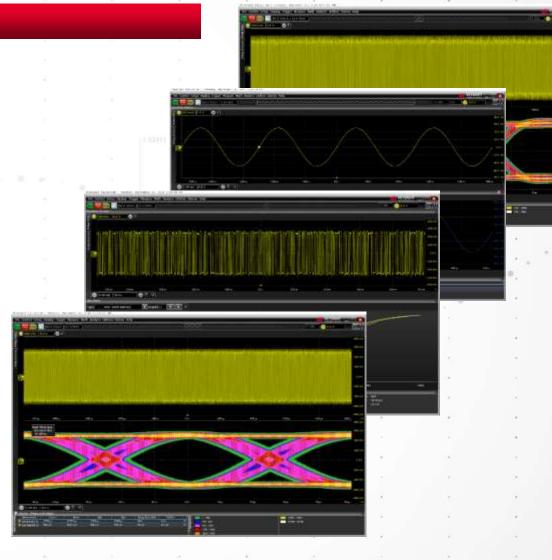

## **Keysight USB4 Test Solution**

# **DP Compliance Program**

- Managed by VESA

- Jim Choate (former Agilent USB Pyramid Lead)

- Why do companies need the logo?

- Ensure interoperability

- Consumers can easily identify compliant products

- How to get it?

- Pass the Compliance Program

- Be a member of VESA

- Sign the VESA DisplayPort Trademark License Agreement

- Authorized Test Centers (ATCs)

- · Allion, GRL, TTA, UL

## **DP Test Point Access**

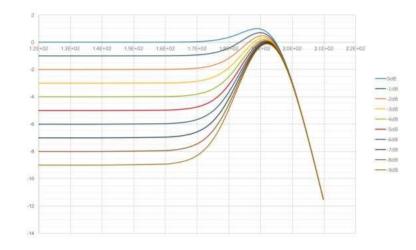

# **DP2.0 Equalization**

DPTX: 3-tap FFE (16 presets)

• DPRX: CTLE (10 DC gain levels) + DFE

• Full characterization  $\rightarrow$  16 x 10 = **160 combinations**

| Preset Number | Pre-shoot [dB] | De-emphasis [dB] | Informative Filter Coefficients |      |                |

|---------------|----------------|------------------|---------------------------------|------|----------------|

|               |                |                  | C-1                             | Co   | C <sub>1</sub> |

| 0             | .0             | 0                | 0                               | 1    | 0              |

| 1             | 0              | -1.9             | 0                               | 0.90 | -0.10          |

| 2             | 0              | -3.6             | 0                               | 0.83 | -0.17          |

| 3             | 0              | -5.0             | 0                               | 0.78 | -0.22          |

| 4             | .0             | -8.4             | 0                               | 0.69 | -0.33          |

| 5             | 0.9            | 0                | -0.05                           | 0.95 | 0              |

| 6             | 1.1            | -1.9             | -0.05                           | 0.86 | -0.09          |

| 7             | 1.4            | -3.8             | -0.05                           | 0.79 | -0.16          |

| 8             | 1.7            | -5.8             | -0.05                           | 0.73 | -0.22          |

| 9             | 2.1            | -8.0             | -0.05                           | 0.68 | -0.27          |

| 10            | 1.7            | 0                | -0.09                           | 0.91 | 0              |

| 11            | 2,2            | -2.2             | -0.09                           | 0.82 | -0.09          |

| 12            | 2.5            | -3.6             | -0.09                           | 0.77 | -0.14          |

| 13            | 3:4            | -6.7             | -0.09                           | 0.69 | -0.22          |

| 14            | 3.8            | -3.8             | -0.13                           | 0.74 | -0.13          |

| 15            | 1.7            | -1.7             | -0.05                           | 0.55 | -0.05          |

The coefficients are normalized such that |C-1| + C<sub>0</sub> + |C<sub>1</sub>| corresponds to full output swing. Preset configuration 15 represents operation mode with lower transmitter swing.

$De - emphasis = 20 \cdot \log 10 \left( \frac{c_{-1} + c_0 + c_1}{c_{-1} + c_0 - c_1} \right)$

2. Preshoot and de-emphasis are calculated as following:  $Preshoot = 20 \cdot \log 10 \left( \frac{-c_{r-1} + c_{r} + c_{r}}{c_{r-1} + c_{r} + c_{r}} \right) \qquad De - e\pi$

14

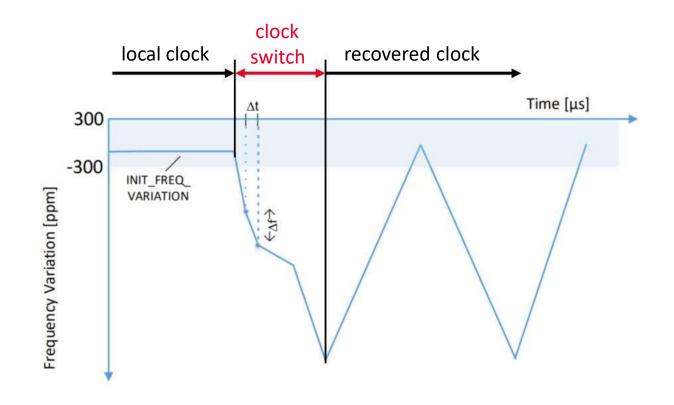

## **LTTPRs**

- LTTPRs are needed as total channel loss increases with PHY rate

- Longer channel

- Extra latency

- Longer and more complex link training

- Clock switch

- During link training

- 8b/10b in transparent mode

- 128b/132b SCR in progress

- Test methodology in development

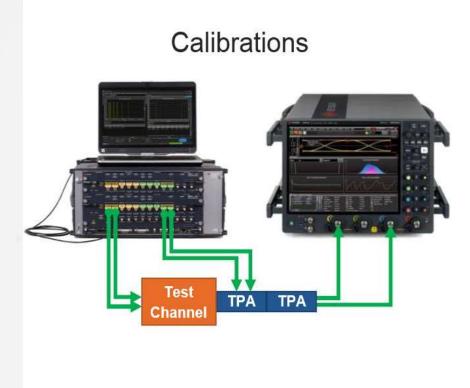

# How to test DP PHY layer?

## Source

- Configure the source to output test patterns with certain drive settings → AUX controller

- Embed worst-case channels, apply equalization on the oscilloscope

- Run measurements

## Sink

- Generate the stress signal with a pattern generator

- Guide the sink through Link Training → AUX controller

- Read built-in error counter

## **DP Source Compliance Test**

#### **SOFTWARE PACKAGES**

Wilder

Keysight

Unigraf

- Updated software package D9040DPPC

- New software package D90xxDPPC

- Productivity improvements

- ANPL

- Disaggregation

**RBR-HBR3**

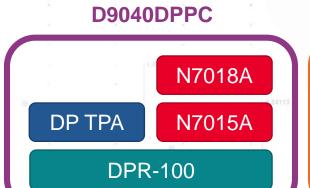

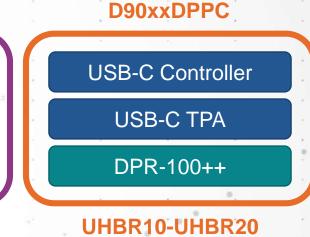

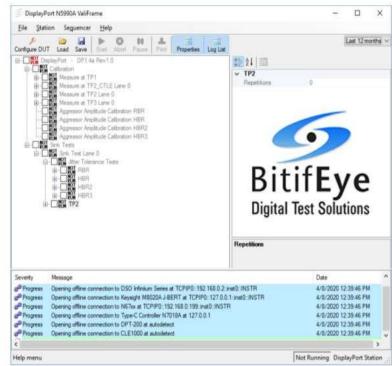

## **DP Sink Compliance Test**

#### SOFTWARE

Wilder

Keysight

Unigraf

- New software package N5991xxxA

- Automated sink calibration and tests

- All PHY rates from RBR to UHBR20

- Standard DP connector and USB Type-C

#### **N5991xxxA**

N7018A

**USB-C Controller**

**DP TPA**

N7015A

**USB-C TPA**

**DPT-200**

DPR-100++

### **RBR-UHBR20**

# **DP Sink Compliance Test**

# Q & A